#### 第一章 概論

- 1.1 邏輯晶片大致上分為標準邏輯(Standard Logic)【例如 TTL 的 74 系列及 54 系列, CMOS 的 40 系列等等】及應用規格積體電路(Application Specific Integrated Circuit; ASIC)

- 1.2 應用規格晶片 (ASIC) 可分為可程式邏輯元件 (PLD)、閘陣列晶片 (Gate Array)、細胞元晶片 (Cell-Based) 及完全訂製型晶片 (Full Custom) 等四類。若考慮成本及開發時間,則 CPLD 最佔優勢,也是為何 CPLD 會越來越受歡迎的原因。

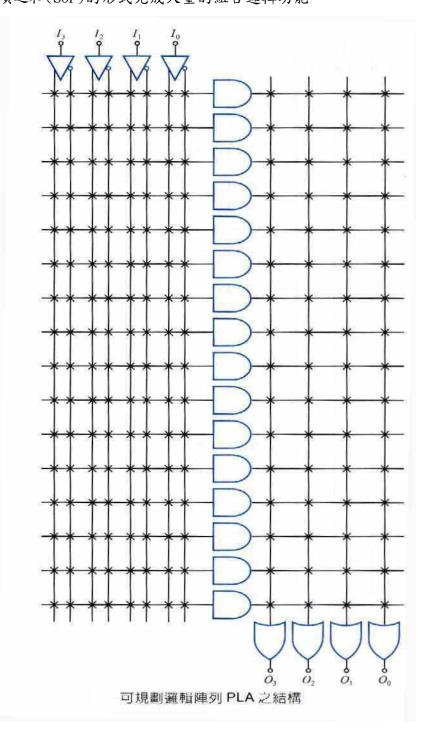

- 1.3 PLD (Programmable Logic Device)可程式邏輯元件 為可程式邏輯元件的總稱,典型的 PLD 由一個可規劃的 AND 陣列和一個可規劃的 OR 陣 列所構成,而任何一個組合邏輯都可用 " **及-或** " 運算式來描述,所以,PLD 能以積 項之和(SOP)的形式完成大量的組合邏輯功能。

#### 其產品有

- ◆ PAL(Programmable Array Logic):為 PLD 最早的產品,只能燒錄一次。

- ◆ EPLD(Erasable PLD):用 CMOS EPROM 技術,故可重覆燒錄,但需使用紫外光線清除資料。

- ◆GAL(Generic Array Logic):應用 EEPROM 技術,可重覆燒錄,且使用電子方式清除資料。

- ◆PEEL(Programmable Electrically Logic):內部結構與 GAL 相似,但可重覆燒錄 1000 次以上,壽命更長更實用。

- 1.4 CPLD (Complex Programmable Logic Device) 複雜可程式邏輯元件 早期多為 EEPROM 的技術背景,基於乘積項(Product term)的結構,可分為

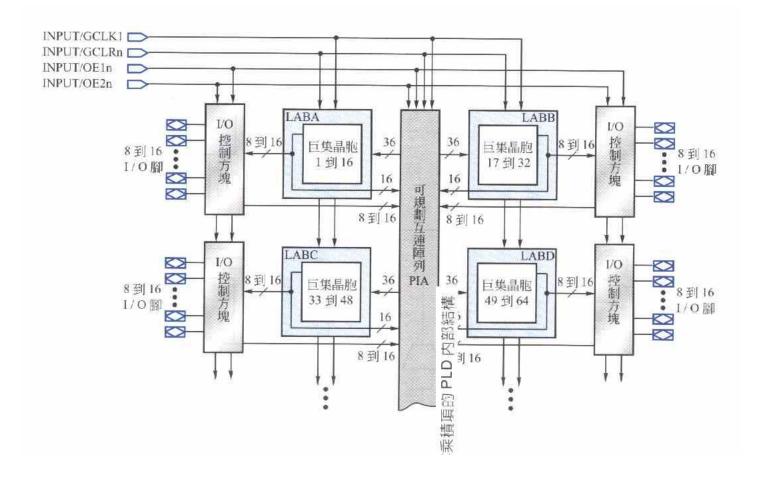

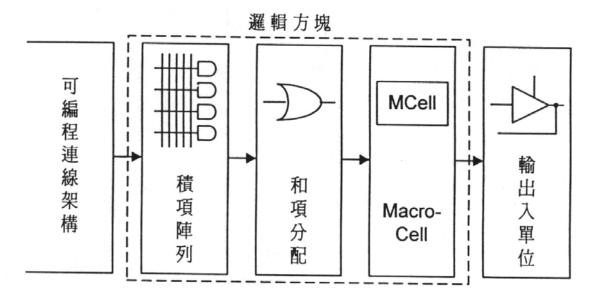

- (1). 巨集晶胞(Macro cell:簡稱 MC),而多個巨集晶胞的集合稱之為邏輯陣列方塊 (LAB),如 Altera MAX3000 系列 EPM3064ALC44-10 就是 64 個 Macrocells(巨集晶胞),44 支接腳,16 個巨集晶胞組成一個邏輯陣列方塊(LAB)共有 4 個邏輯陣列方塊。 (2). 可規劃互連陣列(Programmable Interconnect Array:簡稱 PIA):負責信號的傳遞。

- (3). I/O控制方塊:負責輸入輸出信號的特性控制。

1.5 FPGA (Filed Programmable Gate Array) 現場可程式化閘陣列 CPLD/FPGA 之差別:

FPGA 最早由 Xilinx 公司發明,多為 SRAM 的技術背景,基於查表法 (Look Up Table;簡稱 LUT) 的結構,需外掛配置用的 EPROM (Erasable Programmable Read Only Memory)或 EEPROM (Electrically Erasable Programmable Read Only Memory), Xilinx 公司將 SRAM (Static Random Access Memory)技術(需外掛配置用的 EPROM 或 EEPROM)的 PLD稱為 FPGA,而將 Flash (類似 EEPROM)技術背景,乘積項結構的 PLD稱為 CPLD; Altera把自己的 PLD產品—MAX系列 (EEPROM 技術背景)與 FLEX / ACEX / APEX系列 (SRAM技術背景)都稱為 CPLD,由於 FLEX / ACEX / APEX系列也是 SRAM技術背景,與 Xilinx公司 FPGA 一樣,需外掛配置用的 EPROM或 EEPROM,所以很多人把 FLEX / ACEX / APEX系列也稱為 FPGA。

# ※比較:記憶體

- A: 唯讀記憶體(ROM)-電源消失時,資料可儲存不會消失。

- # PROM→可規劃一次的 ROM, 其記憶體為附有保險絲的二極體矩陣, 由於燒錄後保險絲燒斷, 所以僅能燒錄一次。

- # EPROM→(Erasable programmable ROM),將 PROM 的保險絲改為由 MOSFET 構成的電子開關,故可燒錄可清除(擦拭)資料,清除方法是利用紫外光線照射 15~30分鐘左右。

- # EEPROM→(Electrically Erasable Programmable ROM), 燒錄及清除資料, 皆以電器方式來完成, EEPROM 是利用反向高電壓(12~15V)來清除資料, 只需數秒即可清除資料, 而清除時間與記憶體容量成正比。

- B:隨機存取記憶體(RAM)-電源消失時,資料亦會消失。

- # SRAM → (Static RAM): 靜態隨機存取記憶體,資料存在正反器,資料的存取速度快,但價格貴且體積大,功率消耗大。

- # DRAM→(動態 RAM)價格便宜,體積小耗電量低,常做為電腦的主記憶體,資料存在 閘極與源極之寄生電容上,寄生電容上的電荷會逐漸消失,須在資料不正 確前便予以刷新(refresh)。

- 1.6 CPLD與FPGA具有ISP(In System Program),可直接在電路上隨時規劃燒錄。

1.7 一般來說, PLD 的優點就是速度快、更改容易、易學、不佔空間... 等

## 一、速度快

PLD 的速度就是他的傳播延遲時間短,在高速中也能動作,一般典型值為每週期 50ns,即在 20MHz 的高速仍可動作。

#### 二、更改容易

目前的 PLD 已 CMOS 化,可用電子式清除,因此可以立刻更改程式,對於測試或實驗幫助很大。

## 三、不佔空間

因為一顆 PLD 可以取代數顆 TTL 數位 IC, 所以電路中的 IC 數量自然減少,同時可使印刷電路板的面積相對的縮小,減少佈線及設計時間,又可降低成本。

### 四、簡單易學

若以傳統的數位 IC 組合成一個電路往往需要瞭解各個數位 IC 的功能,初學者容易摸不著邊,但若從 PLD 來學電路設計就容易多了。

五、設計與維護容易。

六、成本降低,可靠性增加。

#### 1.8 晶片供應商

隨著可編程邏輯器件應用的日益廣泛,許多 IC 製造廠家涉足 PLD/FPGA 領域。目前世界上有十幾家生產 CPLD/FPGA 的公司,最大的三家是: ALTERA, XILINX, Lattice,其中 ALTERA 和 XILINX 佔有了 60%以上的市場份額

1。ALTERA: 九十年代以後發展很快,是最大可編程邏輯器件供應商之一。主要產品有:

MAX3000/7000, FLEX10K, APEX20K, ACEX1K, Stratix, Cyclone 等。開發軟體為 MaxplusII 和 QuartusII。

普遍認為其開發工具—MaxplusII 是最成功的 PLD 開發平台之一,配合使用 Altera 公司提供的免費 OEM

HDL 綜合工具可以達到較高的效率。

$2 \circ \underline{XILIXN}$ : FPGA 的發明者,老牌 PLD 公司,是最大可編程邏輯器件供應商之一。產品種類較全,主要有: XC9500/4000,Coolrunner(XPLA3) ,Spartan,Virtex 等。開發軟體為 Foundition 和 ISE。通常來說,在歐洲用 Xilinx 的人多,在日本和亞太地區用 ALTERA 的人多,在美國則是平分秋色。全球 PLD/FPGA 產品 60%以上是由 Altera 和 Xilinx 提供的。可以講 Altera 和 Xilinx 共同決定了 PLD 技術的發展方向。

3。Lattice: Lattice是 ISP 技術的發明者, ISP 技術極大的促進了 PLD 產品的發展,與 ALTERA 和 XILINX 相比,其開發工具比 ALTERA 和 XILINX 略遜一籌。中小規模 PLD 比較有特色,不過其大規模 PLD、FPGA的競爭力還不夠強 1999 年推出可編程類比器件。99 年收購 Vantis(原 AMD 子公司),成為第三大可編程邏輯器件供應商。2001 年 12 月收購 agere 公司(原 Lucent 微電子部)的 FPGA 部門。主要產品有ispLSI2000/5000/8000, MACH4/5, ispMACH4000等

4。ACTEL: 反熔絲(一次性燒寫) PLD 的領導者,由於反熔絲 PLD 抗輻射,耐高低溫,功耗低,速度快, 所以在軍品和航太級上有較大優勢。ALTERA 和 XILINX 則一般不涉足軍品和航太級市場。

5。Cypress : PLD/FPGA 不是 Cypress 的最主要業務,但有一定的用戶群,

6ATME1:PLD/FPGA不是 ATMEL的主要業務,中小規模 PLD做的不錯。ATMEL也做了一些與 Altera和 Xilinx兼容的片子,但在品性上與原廠家還是有一些差距,在高可靠性產品中使用較少,多用在低端產品上。

#### 2 實驗環境

#### 2.1 軟體

(1)、MAX+plus II Baseline 10.2 版 --Altera 公司發展之免費 EDA (Electronic Design Automation) Tools --- MAX + plus II Baseline;可接受繪圖編輯(電路圖)、文字編輯(硬體描述語言)及波形編輯三種設計方式

(2)、Quartus—Altera 公司另一套進階用的 EDA Tools,晶片支援種類較多,功能更強,但操作流程較為繁雜。

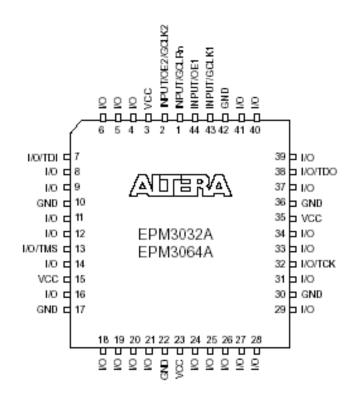

# 2.2 晶片

Altera 公司生產的 MAX3000 系列之 EPM3064ALC44

| Table 1. MAX 3000A Device Features |          |          |          |          |

|------------------------------------|----------|----------|----------|----------|

| Feature                            | EPM3032A | EPM3064A | EPM3128A | EPM3256A |

| Usable gates                       | 600      | 1,250    | 2,500    | 5,000    |

| Macrocells                         | 32       | 64       | 128      | 256      |

| Logic array blocks                 | 2        | 4        | 8        | 16       |

| Maximum user I/O<br>pins           | 34       | 66       | 96       | 158      |

| t <sub>PD</sub> (ns)               | 4.5      | 4.5      | 5.0      | 5.5      |

| t <sub>SU</sub> (ns)               | 2.9      | 2.8      | 3.3      | 3.9      |

44-Pin PLCC

- 3. MAX + plus II Baseline 程式的安裝

- ◆下載程式及執行安裝

- ◆申請 License—需 Email 及硬碟序號

- ◆安裝 Driver—需安裝 Altera ByteBlaster 否則無法使用印表機阜(並列阜 Parallel )LTP1